당신은 주제를 찾고 있습니까 “testout network pro 13.4.8 – 13.4.5 Packet Tracer – Troubleshoot WLAN Issues“? 다음 카테고리의 웹사이트 https://ppa.charoenmotorcycles.com 에서 귀하의 모든 질문에 답변해 드립니다: ppa.charoenmotorcycles.com/blog. 바로 아래에서 답을 찾을 수 있습니다. 작성자 Tech Acad 이(가) 작성한 기사에는 조회수 23,185회 및 좋아요 348개 개의 좋아요가 있습니다.

testout network pro 13.4.8 주제에 대한 동영상 보기

여기에서 이 주제에 대한 비디오를 시청하십시오. 주의 깊게 살펴보고 읽고 있는 내용에 대한 피드백을 제공하세요!

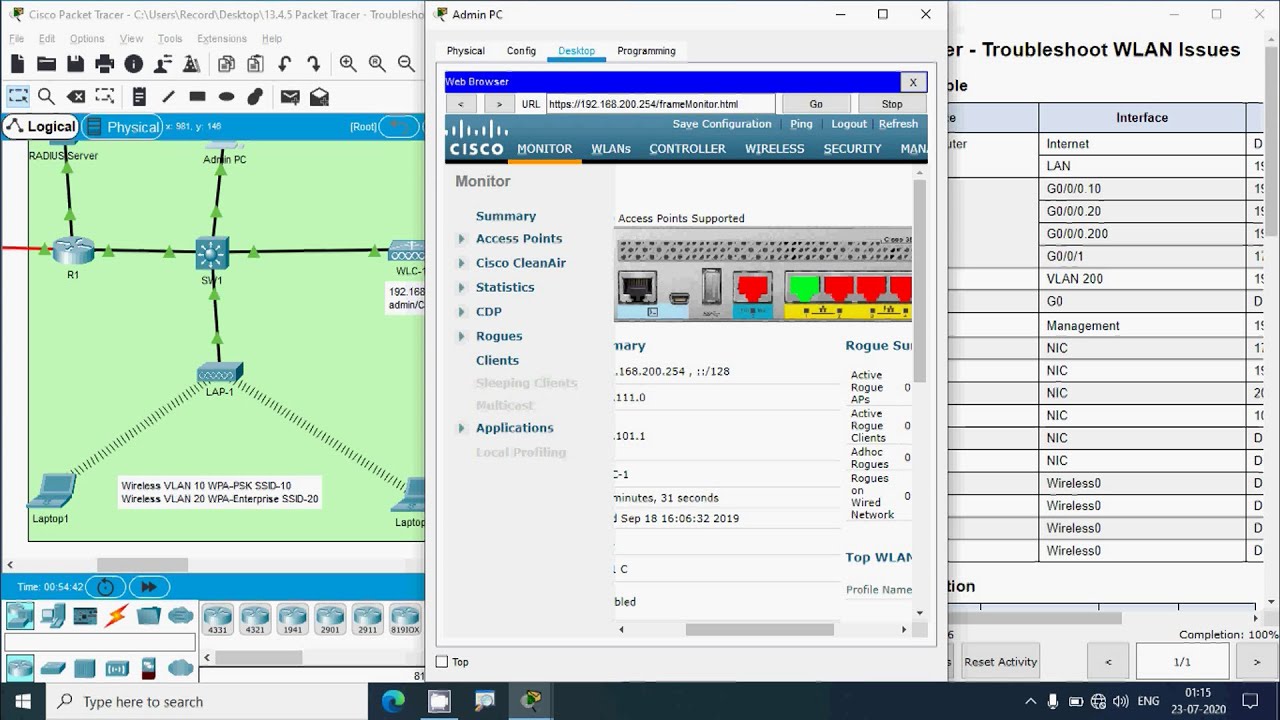

d여기에서 13.4.5 Packet Tracer – Troubleshoot WLAN Issues – testout network pro 13.4.8 주제에 대한 세부정보를 참조하세요

13.4.5 Packet Tracer – Troubleshoot WLAN Issues

CCNAv7 – Switching, Routing, and Wireless Essentials

Visit our Website to contact us: http://www.techacadhelp.com

Follow us on Facebook: https://www.facebook.com/techacad4u

testout network pro 13.4.8 주제에 대한 자세한 내용은 여기를 참조하세요.

TestOut Network Pro – COURSE OUTLINE

0.1.1 Network Pro Introduction (3:35). 0.2 Use the Simulator … TestOut Network Pro Outline – English 5.0.x … 13.4.8 Practice Questions.

Source: www.digiterati.com

Date Published: 8/15/2021

View: 3694

Testout PC Pro Course Outline – Tech Vision Resources

PC Pro Outline … 1.1.1 PC Pro and A+ Certification (9:03) … 13.4.7 Network Troubleshooting Facts 2; 13.4.8 Fix a Network Connection 1 …

Source: database.techvisionresources.com

Date Published: 9/22/2022

View: 4878

User’s Guide – Fujitsu

Windows® 7 Professional … 13.4.8 Encapsulation. … If the specified computer-name does not exist on the network, or if Windows(x64) is not running on the …

Source: software.fujitsu.com

Date Published: 10/30/2021

View: 9765

Full text of “Philips: pm3065 pm3067” – Internet Archive

4 .3 MIL-STD-810 method 516, pro- ced, V MIL-T-28800C par. … sensitivity MTB Sine-wave 13.4.8 80 mV – 10 kHz R4108 MTB gain 1 ms time marker 1 ms 13.4.9 …

Source: archive.org

Date Published: 12/26/2022

View: 1723

d2l-en.pdf – Dive into Deep Learning

Recurrent Neural Network Implementation from Scratch . … 13.4.8 Summary . … we might enumerate all the common events that our pro-.

Source: d2l.ai

Date Published: 8/9/2021

View: 9899

주제와 관련된 이미지 testout network pro 13.4.8

주제와 관련된 더 많은 사진을 참조하십시오 13.4.5 Packet Tracer – Troubleshoot WLAN Issues. 댓글에서 더 많은 관련 이미지를 보거나 필요한 경우 더 많은 관련 기사를 볼 수 있습니다.

주제에 대한 기사 평가 testout network pro 13.4.8

- Author: Tech Acad

- Views: 조회수 23,185회

- Likes: 좋아요 348개

- Date Published: 2020. 7. 25.

- Video Url link: https://www.youtube.com/watch?v=kbjc0_axy0U

Full text of “Philips: pm3065 pm3067”

Full text of “Philips: pm3065 pm3067”